Natures and Disciplines

Disciplines are used to specify the type of a continuous wire (ex: electrical, mechanical, rotational, optical, thermal, etc.). Natures are used to describe the signals used in disciplines.

Natures

A nature is a collection of attributes that are shared by a class of signals. The attributes include the units (units), name used when accessing the signal (access), absolute tolerance (abstol), related natures (ddt_nature, idt_nature), and perhaps user or implementation defined attributes. By convention, the name of a nature begins with a capital letter. The following table lists the natures included in the file disciplines.vams.

Name |

Units |

Access |

Abstol |

Abstol Override |

|

V |

V |

10 -6 |

|

|

A |

I |

10 -12 |

|

|

coul |

Q |

10 -14 |

|

|

Wb |

Phi |

10 -9 |

|

|

A-turns |

MMF |

10 -12 |

|

|

K |

Temp |

10 -4 |

|

|

W |

Pwr |

10 -9 |

|

|

m |

Pos |

10 -6 |

|

|

m/s |

Vel |

10 -6 |

|

|

m/s^2 |

Acc |

10 -6 |

|

|

m/s^3 |

Imp |

10 -6 |

|

|

N |

F |

10 -6 |

|

|

rads |

Theta |

10 -6 |

|

|

rads/s |

Omega |

10 -6 |

|

|

rads/s^2 |

Alpha |

10 -6 |

|

|

N-m |

Tau |

10 -6 |

|

Example:

nature Current

units = "A";

access = I;

abstol = 1p;

idt_nature = Charge;

endnature

The absolute tolerances on the predefined natures can be overwritten by using `define to create a macro with the appropriate name with the desired value.

Example:

`define VOLTAGE_ABSTOL 1e-3

`define CURRENT_ABSTOL 1e-9

`include "disciplines.vams"

Natures can also be derived from other natures, either directly or through a discipline. When doing so it is also possible to override the attributes.

Examples:

nature HighVoltage : Voltage

abstol = 1m;

endnature

nature HighCurrent : electrical.flow

abstol = 1n;

endnature

Disciplines

A discipline is a type used when declaring analog nodes, ports, or branches. They can also be used to declare digital wires and registers. A discipline may include the specification of a domain, either continuous or discrete, and up to two natures. At least one nature is required for continuous disciplines. Continuous disciplines with a single nature are referred to as signal- flow disciplines. Conservative disciplines would two natures. The following table lists the disciplines available from disciplines.vams.

Name |

Potential |

Flow |

Domain |

|

– |

– |

discrete |

|

|

|

continuous |

|

|

– |

continuous |

|

– |

|

continuous |

|

|

|

continuous |

|

|

|

continuous |

|

|

|

continuous |

|

|

|

continuous |

|

|

|

continuous |

|

|

|

continuous |

Example:

discipline electrical

domain continuous;

potential Voltage;

flow Current;

enddiscipline

You declare the discipline of wires simply by giving the discipline followed by a list of wires.

Example:

electrical in, out[3:0];

Continuous time signals belong to the continuous kernel, whereas digital and discrete-event signals belong to the discrete kernel. Signals in the continuous domain are continuous and real valued; signals in the discrete domain can either be binary (0,1, x, or z), integer or real valued and piecewise constant. Unless otherwise specified, the domain of a discipline is taken to be continuous.

The attributes of a nature can be overridden from within a discipline.

Example:

discipline cmos

potential Voltage;

potential.abstol = 10u;

flow Current;

flow.abstol = 100p;

enddiscipline

Compatible Disciplines

Natures associated with the same base nature are compatible. Disciplines are compatible when their corresponding natures are compatible. Branches may only connect nodes with compatible disciplines.

At each node there may be many different values of the absolute tolerance abstol. This may be because the various ports connected to an undeclared node have different, yet compatible, natures for either the potential, the flow, or both. Even if the natures are identical, the value of abstol may be overridden in the discipline of one or more of the ports. In such cases, all of the absolute tolerances must be satisfied at the node. This is equivalent to simply applying the smallest tolerance value for all calculations involving such nodes.

Empty Disciplines

It is possible to define a discipline with no natures. These are known as empty disciplines and they can be used in structural descriptions to let the components connected to a net determine which natures are to be used for the net.

Such disciplines may have a domain binding or they may be domain-less, allowing the domain to be determined by the connectivity of the net.

Example:

discipline interconnect

domain continuous;

enddiscipline

Discipline of Wires and Undeclared Nets

A module can have nets that are undeclared. It might also have discrete nets declared without disciplines. They might be undeclared if they are bound only to ports in module instantiations. They might be declared without disciplines if they are declared using wire types (wire, tri, wand, wor, etc.). In these cases, the net is treated as having an empty discipline. If the net is referenced in behavioral code, then it is treated as having an empty discipline with a domain binding of discrete, otherwise it is treated as having an empty discipline with no domain binding. In these cases the actual discipline used for the net is determined by discipline resolution based on what is connected to the net.

Discipline Resolution

A net can consist of several wires, each existing in different modules and

perhaps each with their own discipline declarations. If within a module a net is

undeclared, it would take its discipline from that to which it is connected.

Occasionally with discrete nets it is not possible to determine a discipline for

a net by what it is connected to or what accesses it, in which case it is

assigned the default discipline (as specified by ` default_discipline ), or

if no default is defined, the empty discipline.

If everything that connects to an undeclared net has the same discipline, then the net will take that discipline. If it connects to ports of different, yet compatible, disciplines, then some additional information is needed to resolve the discipline of the net. However, in the case where the net does not cross domains, it is not necessary to actually resolve the discipline. For discrete nets the discipline is only used when inserting connect modules. For undeclared continuous nets the discipline specifies the units and tolerances of the net. Since only ports with compatible continuous disciplines can be connected to the same net the units are not an issue as compatible disciplines all have the same units. The tolerances are resolved by simply applying all of the tolerances to the net.

There are several situations where it is either desirable or necessary to fully resolve the discipline of an undeclared net. For the cases where all the disciplines associated with a net are compatible, it might be desirable if the default behavior of using the tightest tolerance from any discipline associated with the net is not appropriate. However, in cases where the disciplines are incompatible, the node must be split and connect modules inserted to link the now distinct parts of the newly partitioned node. In this case, the discipline must be fully resolved for each of the new nodes as the resolved discipline is needed when determining the type of connect module that is inserted. A continuous time node cannot be split in this manner, and so all nets of a continuous-time node must be compatible.

The discipline of an undeclared net can be fully resolved with any one of the following methods:

One could explicitly declare the discipline of the net locally.

One could explicitly declare the discipline of the net remotely using hierarchical names. For example:

electrical regulator.drive

would specify the net drive in the instance regulator should have a discipline of electrical.

One could provide connect rules that direct the simulator on how to resolve disciplines when confronted with particular sets of disciplines on a net.

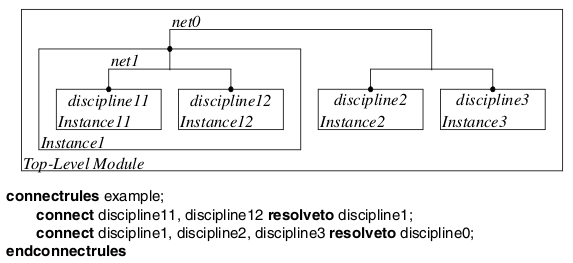

The process of resolving compatible disciplines with the help of connect rules (not available in Verilog-A) is illustrated in the figure below. The process starts at the leaf level modules and proceeds up through the hierarchy to the root or the top-level module. In this example it is assumed that all disciplines are compatible. The first resolution step occurs in Instance1 where the discipline of net1 must be resolved. This net is assumed to be undeclared in Instance1, but it is connected to a port of Instance11, which has a discipline of discipline11, and to a port of Instance12, which has a discipline of discipline12. The first connect rule is used to resolve this net to a discipline of discipline1. This same procedure is used in the top-level module to resolve net0, and the node itself, to a discipline of discipline0.

|